【背景・目的】

・Via firstプロセスでTSVを形成する場合、側壁の絶縁膜は熱酸化を適用

・Via lastプロセスでは先にデバイス面を形成して、さらにサポートガラスに接着剤を用いるため、

絶縁膜には低温で成膜できるP-CVD膜を用いる

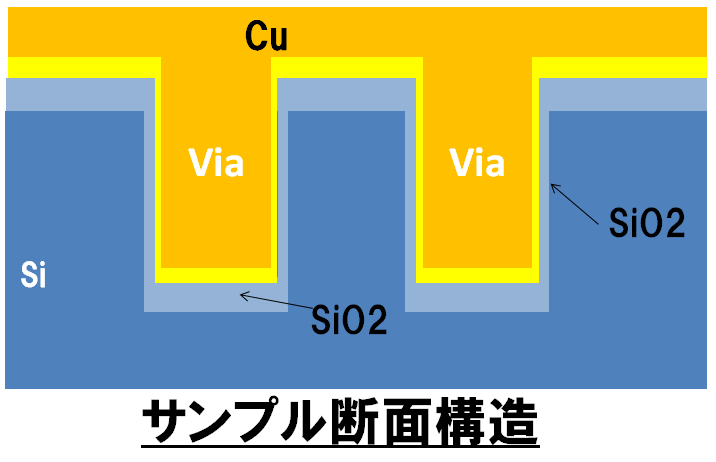

【設計・構造】

■プロセスフロー

・TSV形成 : ホトリソ⇒Siエッチング

・絶縁膜形成 : P-CVD

・シードメタル形成 : Ti + Cu

・ドライフィルム貼付

・ランド形成ホトリソ

・VIAフィルめっき

・ポスト上部平坦化 : Cu CMP

・ドライフィルム剥離

| 膜 種 |

TSV側壁最小膜厚 |

プロセス条件 | |

|---|---|---|---|

| サンプル1 | 熱酸化 |

0.5um |

1000℃/Wet酸化/150min |

| サンプル2 | 120℃レシピTEOS-CVD |

0.5um |

120℃/100Pa/RFパワー680W/5m30s |

| サンプル3 | 120℃レシピTEOS-CVD |

0.3um |

120℃/100Pa/RFパワー680W/3m20s |

| サンプル4 | 150℃レシピTEOS-CVD |

0.5um |

150℃/100Pa/RFパワー620W/5m30s |

| サンプル5 | 150℃レシピTEOS-CVD |

0.3um |

150℃/100Pa/RFパワー620W/3m20s |

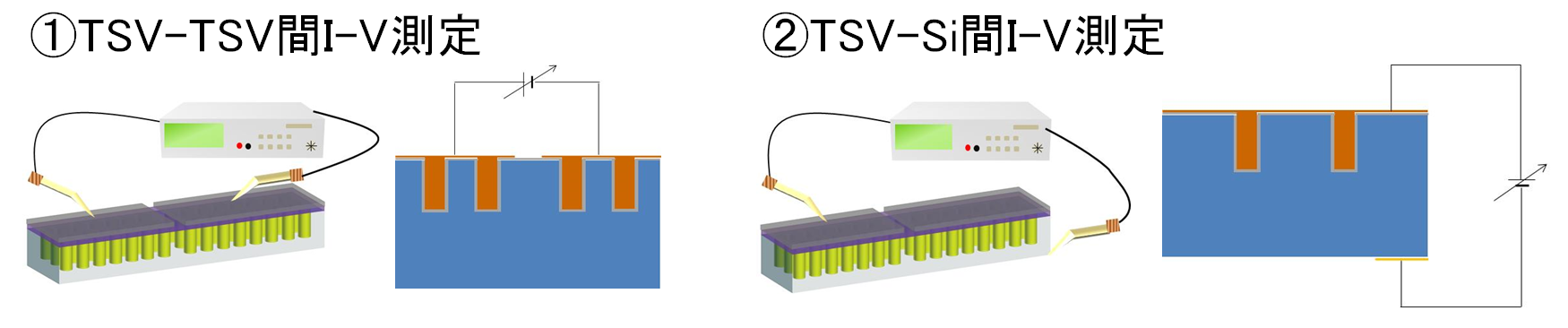

【測定法】

【プロセスポイント】

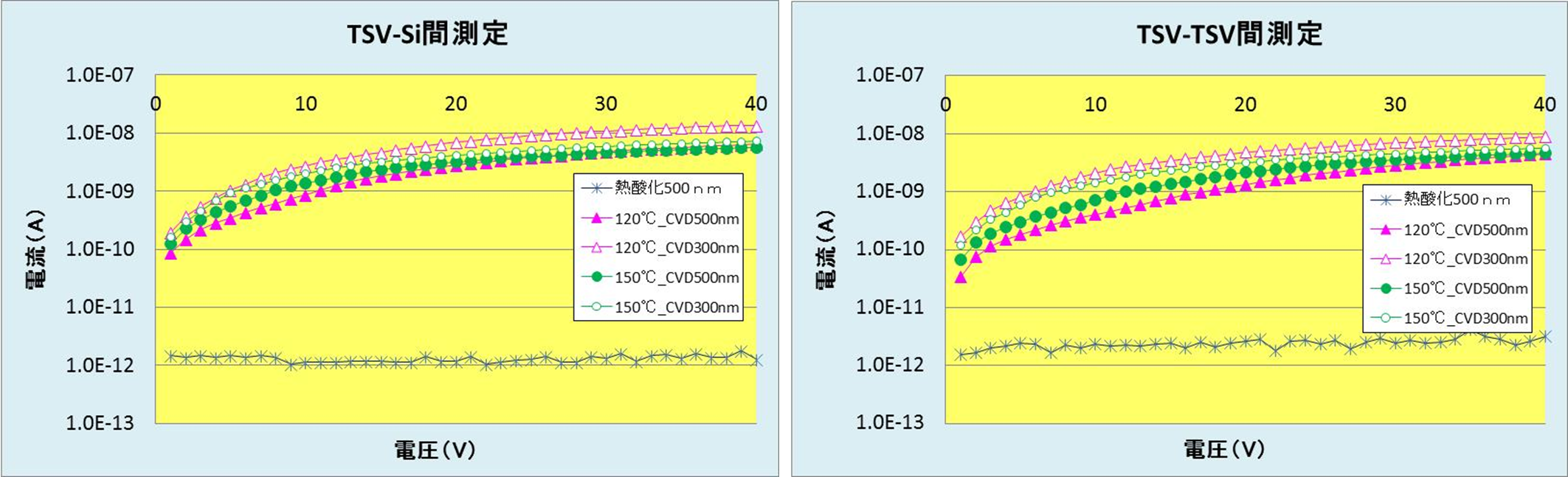

■電気特性(I-V測定)

絶縁性は熱酸化膜には及ばないものの、リーク電流は数nAオーダー

成膜温度による差は膜厚の変化による影響よりも小さい

⇒低温成膜でありながら十分なステップカバレッジと絶縁特性を有する